Мазмұны:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:24.

- Соңғы өзгертілген 2025-01-23 14:51.

Мен бұл нұсқаулықты жазып отырмын, себебі мен VHDL -ге сілтеме жасауды үйрену мен кэш -контроллерді жобалауды бастау қиынға соқты. Мен кэш -контроллерді нөлден бастап ойлап таптым және оны FPGA -да сәтті сынап көрдім. Мен мұнда тікелей картаға түсірілген қарапайым кэш контроллерін ұсындым, сонымен қатар кэш контроллерін тексеру үшін процессорлық жадтың бүкіл жүйесін модельдедім. Бұл нұсқаулық сіздің жеке кэш контроллерлеріңізді құруға сілтеме ретінде пайдалы деп ойлаймын.

1 -қадам: Техникалық сипаттамалар

Бұл біз жобалайтын кэш контроллерінің негізгі сипаттамалары:

- Тікелей карта. (Associated Mapped Cache Controller іздесеңіз осы сілтемеге өтіңіз)

- Бір банкті, кэшті блоктау.

- Жазу хиттері бойынша жазу саясаты.

- Жазбауды жазуға жібермеу немесе айналасына жазу саясаты.

- Жазу буфері немесе басқа оңтайландырулар жоқ.

- Tag Array енгізілген.

Бұдан басқа, біз кэш жады мен негізгі жады жүйесін жасаймыз.

Кэш жадының әдепкі (конфигурацияланатын) сипаттамалары:

- 256 байт бір банкті кэш.

- 16 кэш жолы, әрбір кэш жолы (блок) = 16 байт.

Негізгі жад сипаттамалары:

- Синхронды оқу/жазу жады.

- Көп банкті интерлейлді жады - төрт жады банкі.

- Әр банктің өлшемі = 1 кБ. Демек, жалпы өлшемі = 4 кБ.

- 10 биттік адрестік шинасы бар Word (4 байт) адрестік жады.

- Оқу үшін жоғары өткізу қабілеті. Деректер ені = 16 байтты бір сағат циклінде оқыңыз.

- Мәліметтер енін жазу = 4 байт.

ЕСКЕРТПЕ: егер сіз кэш-контроллердің 4 жақты ассоциативті дизайнын іздесеңіз, менің жаңа нұсқаулықты тексеріңіз

2 -қадам: бүкіл жүйенің RTL көрінісі

Жоғарғы модульдің толық RTL ұсынуы суретте көрсетілген (процессорды қоспағанда). Автобустардың стандартты сипаттамалары:

- Барлық деректер шиналары-32 биттік шиналар.

- Адрестік шина = 32 биттік шина (бірақ мұнда тек 10 бит жады арқылы адрестеледі).

- Деректер блогы = 128 бит (оқуға арналған кең жолақты ені).

- Барлық компоненттер бір сағатпен басқарылады.

3 -қадам: Сынақ ортасы

Жоғарғы модуль құбырсыз процессорды модельдейтін сынақ үстелінің көмегімен сыналды (өйткені бүкіл процессорды жобалау оңай емес !!). Сынақ тақтасы жадқа деректерді оқу/жазу сұрауларын жиі жасайды. Бұл процессормен орындалатын барлық бағдарламаларда кездесетін «Load» және «Store» әдеттегі нұсқауларын мазақ етеді. Сынақ нәтижелері кэш контроллерінің жұмысын сәтті тексерді. Төменде байқалған сынақ статистикасы берілген:

- Барлық оқу/жазу жіберу және жіберу сигналдары дұрыс жасалған.

- Деректерді оқу/жазу операцияларының барлығы сәтті болды.

- Деректердің сәйкес келмеуі/сәйкессіздік проблемалары анықталмады.

- Дизайн Maxm үшін сәтті тексерілді. Жұмыс жиілігі = Xilinx Virtex-4 ML-403 тақтасында 110 МГц (бүкіл жүйе), тек кэш контроллері үшін 195 МГц.

- Негізгі жады үшін блок -оперативті жады шығарылды. Барлық басқа массивтер LUT -те орындалды.

4 -қадам: Қосылған файлдар

Бұл блогта келесі файлдар тіркелген:

- . VHD файлдар кэш контроллері, кэш деректер жиыны, негізгі жад жүйесі.

- Сынақ орындығы.

- Кэш контроллері туралы құжаттама.

Ескертулер:

- Мұнда ұсынылған кэш контроллерінің сипаттамаларын толық түсіну үшін құжаттаманы қараңыз.

- Кодтағы кез келген өзгерістер басқа модульдерге тәуелді. Сондықтан, өзгерістер ақылға қонымды түрде жасалуы керек. Мен берген барлық түсініктемелер мен тақырыптарға назар аударыңыз.

- Егер қандай да бір себептермен Жедел жадты блоктау негізгі жады үшін жасалмаса, жад көлемін кішірейтіңіз, содан кейін файлдар бойынша адрестік шиналар енінің өзгеруі және т.б. Сол жадты LUT немесе таратылған жедел жадыға енгізуге болады. Бұл бағыттау уақыты мен ресурстарды үнемдеуге мүмкіндік береді. Немесе нақты FPGA құжаттамасына өтіңіз және Block RAM үшін сәйкес келетін кодты табыңыз және сәйкесінше кодты өңдеңіз және сол мекенжай шинасының ені сипаттамаларын қолданыңыз. Altera FPGA үшін бірдей әдіс.

Ұсынылған:

VHDL-де кэшті ассоциативті кэш-контроллердің төрт жолды жиынтығының дизайны: 4 қадам

VHDL-дегі қарапайым төрт жолды ассоциативті кэш-контроллердің дизайны: Менің алдыңғы нұсқаулықта біз қарапайым картаға түсірілген кэш-контроллерді қалай жасау керектігін көрдік. Бұл жолы біз бір қадам алға жылжып отырмыз. Біз қарапайым төрт жақты ассоциативті кэш контроллерін жасаймыз. Артықшылығы? Өткізу коэффициенті аз, бірақ баға бойынша

VHDL бағдарламаланатын үзіліс контроллерінің дизайны: 4 қадам

VHDL -де бағдарламаланатын үзіліс контроллерінің дизайны: Мен бұл блогтан алатын жауаптардың түріне таң қаламын. Балалар, менің блогыма кіріп, өз білімдерімді сіздермен бөлісуге ынталандырғаныңыз үшін рахмет. Бұл жолы мен барлық SOC -ларда көретін тағы бір қызықты модульдің дизайнын ұсынамын - Interrupt C

VHDL мен Verilog -та қарапайым VGA контроллерінің дизайны: 5 қадам

VHDL мен Verilog -та қарапайым VGA контроллерінің дизайны: Бұл нұсқаулықта біз RTL -де қарапайым VGA контроллерін құрастырамыз. VGA контроллері - бұл VGA дисплейлерін басқаруға арналған сандық схема. Ол кадрдың буферінен (VGA жады) оқылады, ол көрсетілетін кадрды көрсетеді және қажет етеді

ПХД дизайны қарапайым және қарапайым қадамдармен: 30 қадам (суреттермен)

ПХД дизайны қарапайым және қарапайым қадамдармен: СӘЛЕМ ДОСТАР ПХД дизайнын үйренгісі келетіндер үшін өте пайдалы және қарапайым оқулық басталады

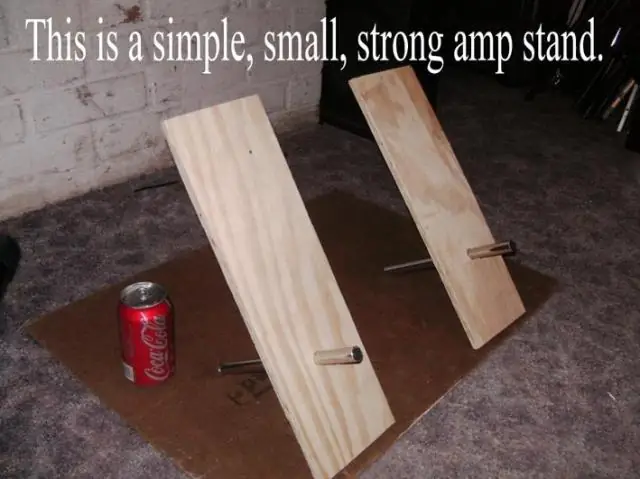

Гитара күшейткіш стенд - «Африкалық орындық» дизайны - қарапайым, кішкентай, күшті, жеңіл, ақысыз немесе нақты арзан: 9 қадам

Гитара күшейткіш стенд - «Африкалық орындық» дизайны - Қарапайым, Кішкентай, Күшті, Оңай, Тегін немесе Нағыз Арзан: Гитаралық амппен тіреуіш - тым оңай - қарапайым, кішкентай, күшті, ақысыз немесе нағыз арзан. Барлық өлшемді күшейткіштер үшін, тіпті бөлек басы бар үлкен шкафтар. Тақталар мен құбырларды өз қалауыңыз бойынша жасаңыз және сізге кез келген қондырғы қажет