Мазмұны:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:24.

- Соңғы өзгертілген 2025-01-23 14:51.

Мен бұл блогтан алатын жауаптардың түріне таң қаламын. Балалар, менің блогыма кіріп, өз білімдерімді сіздермен бөлісуге түрткі болғаны үшін рахмет. Бұл жолы мен барлық SOC -да көретін тағы бір қызықты модульдің дизайнын ұсынамын - Interrupt Controller.

Біз қарапайым, бірақ қуатты бағдарламаланатын үзіліс контроллерін жасаймыз. Бұл толығымен конфигурацияланған және параметрленген дизайн, ол платформаларда тасымалданады. Мен мұны NVIC, 8259a, RISC-V PLIC, Microblaze's INTC сияқты интерактивті контроллер архитектурасында көп оқығаннан кейін жасадым. Бұл блог сізге пайдалы деп үміттенемін және процессор үзілістерді қалай өңдейтінін білуге көмектеседі. үзіліс контроллерінің көмегімен.

1 -қадам: Техникалық сипаттамалар

Төменде IP сипаттамалары берілген:

- AHB3-Lite интерфейсі.

-

Статикалық конфигурацияланатын параметрлер:

- Сыртқы үзіліс көздерінің саны; 63 үзіліске дейін қолдайды.

- Басымдық деңгейлерінің саны; 63 деңгейге дейін қолдайды.

- Ұялау деңгейлерінің саны; ұя салудың 8 деңгейіне дейін қолдайды.

- Автобус ені; 32 немесе 64.

- Жаһандық және жергілікті маскаланатын үзілістер.

- Әр үзіліс үшін динамикалық конфигурацияланатын басымдық деңгейі.

- Екі жұмыс режимі - толық кірістірілген режим және тең басымдық режимі.

- Белсенді жоғары деңгейдегі сезімтал үзілістерді қолдайды.

Дизайнда RISC-V PLIC спецификациясы қол үзу механизмі қолданылады.

Үзілісті алдын ала енгізу 8259а-дан шабыттандырылған

Басқа оқулар: Microblaze INTC, NVIC

2 -қадам: PIC шолуы

Бағдарламаланатын үзіліс контроллері (PIC) сыртқы перифериялық қондырғылардан бірнеше үзіліс алады және оларды мақсатты процессор ядросына бір үзіліс шығысына біріктіреді.

PIC бақылау және күй регистрлері арқылы бақыланады. Барлық PIC регистрлері жадымен салыстырылады және оларға AHB3-Lite шиналық интерфейсі арқылы қол жеткізіледі.

Тіркеу банкі конфигурация регистрінен, қосу регистрлерінен, күтудегі регистрлерден, қызмет регистрлерінен, басымдық регистрлерінен және үзіліс контроллерлеріне тән жеке куәліктер регистрінен тұрады.

Конфигурация регистрі PIC жұмыс режимін орнату үшін қолданылады. Ол толық кірістірілген режимде немесе тең басымдық режимінде жұмыс істей алады.

Әр үзіліске басымдылықтар тағайындалуы мүмкін және жеке бүркемеленуі мүмкін. Барлық үзілістерді жаһандық маскировкаға да қолдау көрсетіледі.

Тіркеу банкі күтілетін үзілістердің басымдықтарын шешу және тиісінше процессорға үзілісті бекіту үшін Priority Resolver және BTC (Binary-Tree-Comparator) -мен өзара әрекеттеседі. Идентификаторлық регистрде үзілістегі ең маңызды басымдықтың идентификаторы бар.

3 -қадам: RTL жобалау және енгізу

PIC дизайнының басымдықтарды шешудің кідірісін төмендетуге бағытталған, бұл дизайнның ең маңызды бөлігі. Дизайн басымдықтарды бір сағаттық циклде шешетіндіктен, Log2 күрделілігі бар көздер санының өсуімен өнімділік нашарлайды.

Дизайн сәтті енгізілді және Artix-7 FPGA-да келесі жиіліктерге дейін уақыт тексерілді.

- 15 көзге дейін: 100 МГц

- 63 көзге дейін: 50 МГц

Тек PIC қосқан үзіліс кідірісі - 3 сағаттық цикл (Процессордың контекстік ауысу уақыты мен бірінші ISR нұсқауларын алу уақытын қоспағанда).

4 -қадам: Маңызды ескертулер мен тіркелген файлдар

Маңызды ескертулер:

- Егер AHB3-Lite интерфейсі қажет болмаса, сіз жоғарғы модульді өзгерте аласыз және PIC қаңқалық дизайнын қолдана аласыз. Алайда, тестілеу орындығы AHB3-Lite интерфейсі бар IP-ге арналған.

- PIC IP v1.0 - бұл толығымен портативті, жалаңаш RTL дизайны.

- Екі режимде де жұмыс істеу үшін функционалды түрде тексерілген.

Қосылған файлдар:

- VHDL -де жобалау кодтары мен тест алаңы.

- Толық IP құжаттары.

Бұл ашық көзден жасалған дизайн. Пайдалануға болады …

Кез келген сұраулар үшін, кез келген уақытта:

Миту Радж

Ұсынылған:

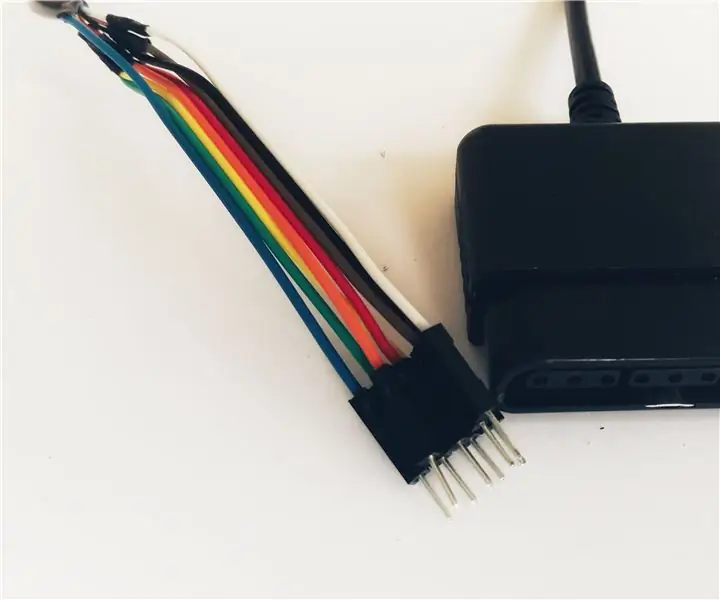

Arduino интерфейсіне арналған PS2 контроллерінің үзіліс адаптері: 10 қадам

PS2 Controller Breakout адаптері Arduino Interfacing үшін: PlayStation 2 контроллері робототехника жобалары үшін өте пайдалы геймпад. Бұл арзан, қол жетімді (екінші қолмен), көптеген түймелер бар және Arduino -мен үйлесімді! Оны пайдалану үшін сізге сымды қосатын арнайы қосқыш қажет

VHDL-де кэшті ассоциативті кэш-контроллердің төрт жолды жиынтығының дизайны: 4 қадам

VHDL-дегі қарапайым төрт жолды ассоциативті кэш-контроллердің дизайны: Менің алдыңғы нұсқаулықта біз қарапайым картаға түсірілген кэш-контроллерді қалай жасау керектігін көрдік. Бұл жолы біз бір қадам алға жылжып отырмыз. Біз қарапайым төрт жақты ассоциативті кэш контроллерін жасаймыз. Артықшылығы? Өткізу коэффициенті аз, бірақ баға бойынша

VHDL -де қарапайым кэш контроллерінің дизайны: 4 қадам

VHDL -дегі қарапайым кэш -контроллердің дизайны: Мен бұл нұсқаулықты жазып отырмын, себебі кэш -контроллерді үйрену мен жобалауды бастау үшін VHDL -ге сілтеме жасау қиынға соқты. Мен кэш -контроллерді нөлден бастап ойлап таптым және оны FPGA -да сәтті сынап көрдім. Менде п

VHDL -де I2C Master дизайны: 5 қадам

VHDL -дегі I2C шеберінің дизайны: Бұл нұсқаулықта VHDL -де қарапайым I2C шеберінің дизайны талқыланады. ЕСКЕРТПЕ: толық кескінді көру үшін әр суретті басыңыз

VHDL мен Verilog -та қарапайым VGA контроллерінің дизайны: 5 қадам

VHDL мен Verilog -та қарапайым VGA контроллерінің дизайны: Бұл нұсқаулықта біз RTL -де қарапайым VGA контроллерін құрастырамыз. VGA контроллері - бұл VGA дисплейлерін басқаруға арналған сандық схема. Ол кадрдың буферінен (VGA жады) оқылады, ол көрсетілетін кадрды көрсетеді және қажет етеді