Мазмұны:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:24.

- Соңғы өзгертілген 2025-01-23 14:51.

Бұл нұсқаулықта біз RTL -де қарапайым VGA контроллерін құрамыз. VGA контроллері - бұл VGA дисплейлерін басқаруға арналған сандық схема. Ол кадрдың буферінен (VGA жады) оқылады, ол көрсетілетін кадрды көрсетеді және дисплей мақсатында қажетті деректер мен синхрондау сигналдарын шығарады.

Егер сіз Verilog/System верилог кодын іздесеңіз: Менің блогыма кіріңіз VGA контроллері мен бейне жүйесі Verilog.

1 -қадам: VGA контроллерінің интерфейсі

Төменде VGA контроллеріндегі негізгі интерфейс сигналдары берілген

- Pixel Clock немесе VGA сағаты

- HSYNC және VSYNC сигналдары

Таңдалған VGA дисплейі үшін алдымен оны басқаруға қажетті Pixel Clock жиілігін есептеу керек. Ол 3 параметрге байланысты: Жалпы көлденең пиксельдер, жалпы тік пиксельдер, экранды жаңарту жиілігі.

Әдетте, F = THP * TVP * жаңарту жиілігі

Әр түрлі VGA дисплейлері үшін қажетті пиксельдік сағаттардағы құжаттарды RAR -дан табыңыз.

HSYNC және VSYNC сигналдары Pixel сағатынан жасалады. HSYNC және VSYNC сигналдарының уақыты параметрлер санына байланысты: көлденең және тік алдыңғы, көлденең және вертикальды көлденең, көлденең және тік дисплей пикселдері, көлденең және тік синхрондау импульстерінің ені мен полярлықтары.

Бұл параметрлер таңдалған VGA дисплейі үшін стандартталған. Бұл құжаттарды RAR қосымшасынан табыңыз.

Бұл параметрлер біздің VGA контроллері IP -де конфигурацияланатын параметрлер.

2 -қадам: VGA дисплейі бар VGA контроллерін біріктіру

Суретте VGA контроллерін VGA дисплейімен қалай біріктіру керектігі көрсетілген. Жүйені аяқтау үшін сізге тағы екі компонент қажет:

- Кадрлық буфер: Көрсетілетін кадрды сақтайтын жад.

- Бейне DAC: RGB цифрлық деректерін түрлендіретін және VGA дисплейін RGB аналогты сигналдармен кернеудің тиісті деңгейінде басқаратын DAC.

Ең қарапайым және танымал бейне DAC -тің бірі - ADV7125. Бұл RGB цифрлық сөздерін 0-0.7 В аналогтық сигналдарға түрлендіретін және VGA дисплейін басқаратын 8 биттік DAC.

3 -қадам: жақтау буферінің дизайны

Бұл көрсетілетін суретті «сақтайтын» жады. Бұл әдетте RAM немесе кейде ROM. Біз кескінді көрсету үшін жақтау буферін қалай жасау керектігін талқылаймыз. Frame буфері бұл сандық ақпаратты VGA контроллерінің командасы бойынша Video DAC -ке жібереді.

Алдымен біз қажетті пиксель тереңдігін анықтауымыз керек. Ол кескіннің сапасын, пиксель көрсете алатын түстердің әртүрлілігін анықтайды. 8-разрядты DAC үшін біз пикселдің негізгі түс компоненттерін көрсетуіміз керек: R, G және B әрқайсысы 8 бит. Бұл дегеніміз, пиксель 24 биттік.

Әрбір пиксель Frame Buffer жадының орындарында іргелес түрде сақталады.

Көрсетілетін сурет 800x600 пиксель делік.

Сондықтан Frame Buffer 800x600 = 480000 x 24 бит жады қажет

Жадтың жалпы көлемі 800x600x24 = 1400 кБ шамамен.

Егер ақ -қара сурет болса, 800x600x1 = 60 кБ шамамен.

Блоктық оперативті жадтар Xilinx FPGA -де Frame Bufer -ті көрсету үшін қолданылған болуы мүмкін.

4 -қадам: Ескертулер

- Таңдалған DAC -ке байланысты VGA контроллерінде қосымша сигналдар қажет. Мен ADV7125 қолдандым.

- VGA дисплейін жүргізер алдында VSYNC және HSYNC бойынша флип-флоптар арқылы циклдік кідірістерді қосыңыз. Бұл DAC және жадтың кешігуіне байланысты. Пиксельдік сигналдарды HSYNC және VSYNC синхрондау керек. Менің жағдайда бұл 2 циклдік кідіріс болды.

- Егер блок өлшемі шектеулі болғандықтан, берілген өлшемдегі кадрлық буфер FPGA -да жасалмаса, суретті көрсету үшін кішірек жадты пайдаланыңыз және кодты толық кадрдың шекарасына емес, қол жетімді жадтың шекарасына айналдыру үшін өңдеңіз. Бұл бүкіл суреттің бойында бірдей суретті қайталайды. Басқа әдіс - бұл пиксельді масштабтау, онда әр пиксель толық кескінді толық экранда, аз ажыратымдылықта көрсету үшін қайталанады. Мұны кодтағы адрестерді көбейту логикасын өзгерту арқылы жасауға болады.

- IP барлық FPGA-да толығымен тасымалданады және Virtex-4 FPGA-да 100 МГц-ге дейін уақытты тексереді.

5 -қадам: Қосылған файлдар

RAR құрамында:

- VGA контроллері коды

- PDF форматында VGA стандарттары.

Ұсынылған:

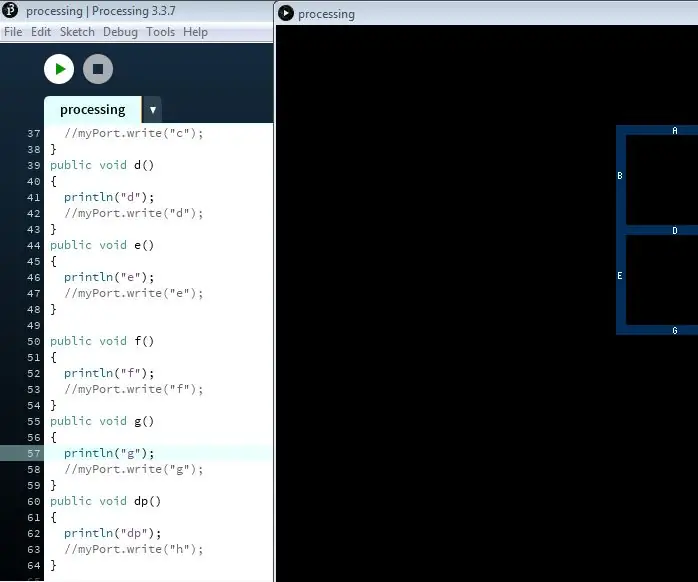

Өңдеу мен Arduino мен 7 сегменті мен сервистік GUI контроллерін қосу: 4 қадам

Processing and Arduino мен Make 7 Segment and Servo GUI контроллерін қосу: Кейбір жобалар үшін сізге Arduino -ны қолдану қажет, себебі ол прототиптеудің оңай платформасын ұсынады, бірақ Arduino -ның сериялық мониторында графиканы көрсету өте ұзақ уақытты қажет етеді және тіпті қиын. Сіз Arduino сериялық мониторында графиктерді көрсете аласыз

VHDL бағдарламаланатын үзіліс контроллерінің дизайны: 4 қадам

VHDL -де бағдарламаланатын үзіліс контроллерінің дизайны: Мен бұл блогтан алатын жауаптардың түріне таң қаламын. Балалар, менің блогыма кіріп, өз білімдерімді сіздермен бөлісуге ынталандырғаныңыз үшін рахмет. Бұл жолы мен барлық SOC -ларда көретін тағы бір қызықты модульдің дизайнын ұсынамын - Interrupt C

VHDL -де қарапайым кэш контроллерінің дизайны: 4 қадам

VHDL -дегі қарапайым кэш -контроллердің дизайны: Мен бұл нұсқаулықты жазып отырмын, себебі кэш -контроллерді үйрену мен жобалауды бастау үшін VHDL -ге сілтеме жасау қиынға соқты. Мен кэш -контроллерді нөлден бастап ойлап таптым және оны FPGA -да сәтті сынап көрдім. Менде п

DHT11 температура сенсорын Arduino мен басып шығару температурасы мен жылу мен ылғалдылықта қалай қолдануға болады: 5 қадам

DHT11 температура сенсоры Arduino мен басып шығару температурасы бар жылу мен ылғалдылықта қалай қолданылады: DHT11 сенсоры температура мен ылғалдылықты өлшеу үшін қолданылады. DHT11 ылғалдылық пен температура сенсоры электрониканың өте танымал әуесқойлары, DIY электроникасының жобаларына ылғалдылық пен температура туралы мәліметтерді қосуды жеңілдетеді. Бұл әр

ПХД дизайны қарапайым және қарапайым қадамдармен: 30 қадам (суреттермен)

ПХД дизайны қарапайым және қарапайым қадамдармен: СӘЛЕМ ДОСТАР ПХД дизайнын үйренгісі келетіндер үшін өте пайдалы және қарапайым оқулық басталады