Мазмұны:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:23.

- Соңғы өзгертілген 2025-01-23 14:51.

AmCoderhttps бойынша: //www.linkedin.com/in/mituFollow Автордың толығырақ:

Миту Радж - жай әуесқой және үйренуші - чип дизайнері - бағдарламалық жасақтама жасаушы - физика мен математиканың энтузиастары AmCoder туралы толығырақ »

## Бұл синус пен косинус толқынын генерациялау үшін CORDIC ALGORITHM -ді VHDL енгізу үшін Google -де ең көп басылған, танымал сілтеме ## Қазіргі уақытта көптеген аппараттық тиімді алгоритмдер бар, бірақ олар бағдарламалық қамтамасыз ету жүйелерінің үстемдігіне байланысты жақсы белгілі емес. көп жылдар. CORDIC - бұл белгілі бір тригонометриялық, гиперболалық, сызықтық және логарифмдік функцияларды қоса алғанда, кең ауқымды функцияларды есептеу үшін қолданылатын ауысу мен қосу логикасының жиынтығынан басқа ештеңе емес алгоритм. Бұл калькуляторларда қолданылатын алгоритм және т. Осылайша, қарапайым ауыстырғыштар мен қосқыштарды қолдану арқылы біз корпустық алгоритмді қолдана отырып, күрделілігі аз, бірақ DSP қуаты бар аппаратураны жобалай аламыз. Сондықтан оны VHDL немесе Verilog -та арнайы жылжымалы нүктелік қондырғыларды немесе күрделі математикалық IP -лерді пайдаланбай RTL -дің жалаңаш дизайны ретінде жасауға болады.

1 -қадам: VHDL және Modelsim

Бұл жерде синхронды және позалық толқын генерациялау үшін VHDL көмегімен кордикалық алгоритм жүзеге асады. Ол синусын және кіріс бұрышының косинусын үлкен дәлдікпен шығара алады. Код FPGA -да синтезделеді. Modelsim конструкциясы мен сынақ үстелін модельдеу үшін қолданылады.

2 -қадам: Дизайн мен сынақ үстеліне арналған VHDL коды

Жылжымалы нүктелік сандарды бейнелеу үшін екілік масштабтау әдісі қолданылады.

Код жасамас бұрын, берілген құжаттарды қараңыз.

Go thruSimulating cordic_v4.vhd - Дизайн - Кіріс - 32 биттегі бұрыш + белгі биті; ол 0.000000000233 градус дәлдікпен 0-ден +/- 360 градусқа дейінгі кез келген бұрышты өңдей алады. Енгізу кезінде -> MSB -бұл белгі биті, ал қалған 32 биттік шаманы көрсетеді. 0,00001526 дәлдікпен. Назар аударыңыз, егер тиісті синус немесе cos мәні теріс болса, шығыс 2 комплимент түрінде көрсетіледі. Testb.vhd имитациясы - Дизайн үшін сынақ стендісі (1) Кіріс бұрыштары мен тартылу ысырмасы = '0'. Модельдеудің екі қадамынан кейін «1» қалпына келтіріңіз және «барлығын іске қосыңыз.» дұрыс.

3 -қадам: файлдар тіркелді

(1) cordic_v4.vhd - Дизайн. (2) testb.vhd - Дизайнға арналған орындық.

(3) Бұрыштық кірістерді мәжбүрлеу және екілік нәтижелерді түрлендіру туралы құжат.

Жаңарту: БҰЛ ФАЙЛДАР САҚТЫ БОЛМАЙДЫ ЖӘНЕ БІР КӨРСЕТІЛМЕЙДІ. КЕЛЕСІ ҚАДАМДАН ФАЙЛДАРДЫ ПАЙДАЛАНЫҢЫЗ

4 -қадам: Mini -Cordic IP Core - 16 биттік

Жоғарыда келтірілген шектеулер бір сағаттық циклде есептеулер жүргізуге байланысты баяу, төмен жұмыс жиілігінде.

- Өнімділікті жақсарту үшін бірнеше циклге бөлінген маңызды жолдар.- Жылдамырақ- FPGA дәлелденген дизайны 100 МГц жиілікке дейін синтезделген.- HDL, аз жабдықта оңтайландырылған көбірек аймақ.- Жүктеу және орындалу күйі сигналдары. алдыңғы. Testbench:

0 -ден 360 градусқа дейінгі бұрыштық кірістер толығымен автоматтандырылған

Тіркелген файлдар: 1) мини кордич vhdl файлы2) мини кордтық сынақ стенді 3) Mini Cordic IP Core нұсқаулығы 4) Бұрыштарды қалай мәжбүрлеу және нәтижелерді түрлендіру туралы құжат

Барлық сұрақтар бойынша менімен хабарласыңыз:

Миту Радж

мені қадағалаңыз:

пошта: iammituraj@gmail.com

### Жүктеулер саны: 325 01-05-2021 дейін ###

### Код соңғы өңделген: 07-2020 жылдың шілдесі ###

Ұсынылған:

Өзін -өзі теңестіретін робот - PID бақылау алгоритмі: 3 қадам

Өзін -өзі теңдестіру роботы - PID бақылау алгоритмі: Бұл жоба ойластырылды, себебі мен басқару алгоритмдері мен функционалды PID ілмектерін қалай тиімді енгізу туралы көбірек білгім келді. Жоба әзірге даму сатысында, өйткені Bluetooth модулі әлі қосылмайды

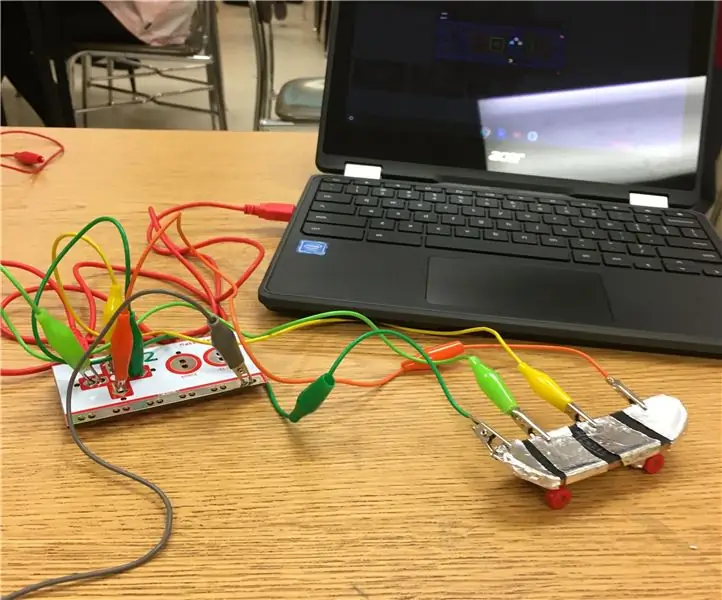

Техникалық палубамен Makey Makey қолданудың қарапайым әдісі: 5 қадам

Техникалық палубамен Makey Makey қолданудың қарапайым әдісі: Сәлеметсіз бе. Мен жақында осы байқауда технологиялық палубаны жасайтын макей бағдарламасын көрдім, ол өте керемет, бірақ қиын болып көрінді, сондықтан мен технологиялық палубамен ойын ойнаудың жеңіл әдісін жасадым. Егер сізге менің нұсқауым ұнайтын болса, макей макей байқауында оған дауыс беріңіз

Үстел ойыны Жасанды интеллект: минимакс алгоритмі: 8 қадам

Үстел ойыны жасанды интеллект: минимакс алгоритмі: Сіз шахмат немесе дойбыға қарсы ойнайтын компьютерлер қалай жасалынғанын ойлап көрдіңіз бе? Нұсқаулықтан басқа ештеңеге қарамаңыз, ол сізге Minimax алгоритмін қолдана отырып қарапайым, бірақ тиімді жасанды интеллект (АИ) жасауды көрсетеді! Th пайдалану арқылы

Эллипсті қолданудың тамаша ханым техникасы: 4 қадам

Эллипсті қолданатын тамаша ханым бояу техникасы: Мен сізге осындай нәрсені жасау техникасын қалай қолдану керектігін көрсетемін: (сапасы нашар)

Қолданудың жақсартылған қарапайым медиа орталығы мен қашықтан басқару: 6 қадам

Қарапайым медиаорталық және қолдануды жақсартатын қашықтан басқару пульті: Иә, бұл ДК-ге негізделген басқа да медиа-орталық (немесе HTPC), бірақ бір ерекшелігі бар: оны басқару оңай, осылайша егде жастағы адамдарға, мүгедектерге өте ыңғайлы, немесе жай жалқау пайдаланушылар. Уикипедиядан: “