Мазмұны:

- 1 -қадам: Блок диаграммасы

- 2 -қадам: жұмыс принципі

- 3 -қадам: Логиканы енгізу

- 4 -қадам: тығырықтан шығу

- 5 -қадам: құрылғы конфигурациясы - Matrix0 схемасы

- 6 -қадам: Құрылғыны конфигурациялау - SPI Clocking Logic

- 7 -қадам: құрылғы конфигурациясы - Matrix0 компоненттерінің қасиеттері

- 8 -қадам: құрылғы конфигурациясы - Matrix1 схемасы

- 9 -қадам: құрылғы конфигурациясы - 3 биттік екілік санауыш

- 10 -қадам: Құрылғы конфигурациясы - 3 биттік салыстыру логикасы

- 11 -қадам: Құрылғыны конфигурациялау - сандық салыстыру логикасы және уақытша тіркеу

- 12 -қадам: Құрылғы конфигурациясы - Matrix1 компоненттерінің қасиеттері

- 13 -қадам: Нәтижелер

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:23.

- Соңғы өзгертілген 2025-01-23 14:51.

Басқару жүйелері мен онымен байланысты құрылғылар бірнеше қуат көздерімен жұмыс істейді, мысалы, ауытқу сызықтары немесе аккумуляторлар, және берілген жиынтықтағы ең жоғары (немесе ең төменгі) сызықты қадағалауы керек.

Мысалы, «көп аккумуляторлы» қуатты жүйеде жүктемені ауыстыру үшін жүйеде аккумуляторлық массив арасындағы минималды немесе максималды кернеуді бақылау қажет (арнайы коммутация алгоритмінің функциясы ретінде max немесе min) және жүктемені динамикалық түрде бағыттау. нақты уақыттағы ең қолайлы ақпарат көзі. Немесе дұрыс зарядтау үшін жүйеге ең төменгі кернеулі батареяны уақытша ажырату қажет болуы мүмкін.

Тағы бір мысал - қазіргі заманғы күн энергиясы жүйесі, онда әрбір күн панелі тілтротат механизмімен және күнді бақылау схемасымен жабдықталған (соңғысы панельді бағдарлау үшін Күннің орналасуы туралы ақпаратты береді). Максималды кернеу туралы ақпаратпен күн батареясының әрбір позициясын шын мәнінде ең жоғары шығыс кернеуін беретін сым тақтасы негізінде дәл баптауға болады, осылайша қуатты оңтайландырудың жоғары деңгейіне жетуге болады.

Коммерциялық IC -дің бірнеше маркалары бар (негізінен микроконтроллерлер), олар максималды кернеуді қадағалаушыны қолдана алады. Дегенмен, олар бағдарламалауды қажет етеді және аралас сигналды шешімге қарағанда экономикалық тиімділігі төмен. Dialog GreenPAKTM дизайнын толықтыру дизайнның қол жетімділігіне, өлшемі мен модульділігіне оң әсер етуі мүмкін. Бұл дизайн аналогты да, цифрлық схеманы да бір чипке біріктірудің артықшылығын пайдаланады.

Бұл нұсқаулықта сегіз түрлі көздер арасында максималды (немесе ақырында мин) кернеуді табуға қажет аналогтық фронтальды және цифрлық логика жүзеге асырылады.

Аналогты максималды/мин 8 каналды енгізу үшін SLG46620G қолданылады.

Төменде біз 8 каналды аналогтық максималды/мин кернеу мониторын құру үшін шешім қалай бағдарламаланғанын түсіну үшін қажет қадамдарды сипаттадық. Алайда, егер сіз бағдарламалаудың нәтижесін алғыңыз келсе, GreenPAK бағдарламалық жасақтамасын жүктеп алып, аяқталған GreenPAK дизайн файлын қараңыз. GreenPAK әзірлеу жинағын компьютерге қосыңыз және 8 каналды аналогтық максималды/мин кернеу мониторын жасау үшін бағдарламаны басыңыз.

1 -қадам: Блок диаграммасы

1 -суретте енгізілген жүйенің жаһандық диаграммасы көрсетілген.

8 айнымалы кернеу көзінің тізбегі басқаларға қарағанда ең жоғары кернеулі көзді таңдауға қабілетті теңшелген ішкі дизайнға қосылған GreenPAK ADC модуліне мультиплексирленген және интерфейске қосылған. Ішкі логика бұл ақпаратты көрсету немесе одан әрі өңдеу үшін шығарады.

Дизайн GreenPAK SLG46620G өніміне негізделген, себебі ол барлық қажетті аналогтық және цифрлық құрылыс блоктарын енгізеді. Бұл жағдайда массив GreenPAK IC тікелей басқаратын ADG508 аналогтық мультиплексоры арқылы сканерленеді.

Шығу ақпараты-бұл максималды кернеу кезіндегі кернеудің бастапқы санына сәйкес келетін 3-разрядты сан. Бұл ақпаратты алудың тікелей жолы-нөмірді 7 сегментті дисплей арқылы көрсету. SLG46620G сандық шығысын Reference-де сипатталған GreenPAK шешімі сияқты 7 сегментті дисплей драйверіне немесе жалпы 74LS47 IC интерфейсіне қосу арқылы оңай жасауға болады.

Ұсынылған схема максималды кернеуді іздейді. Дизайнды минималды кернеуді табуға айналдыру үшін аналогтық мультиплексор мен GreenPAK аналогтық кірісі арасында мультиплексордың шығуын 1 В кернеу кернеуінен шегеріп, қарапайым алдын ала кондиционерлеу схемасын қосу қажет.

2 -қадам: жұмыс принципі

Дизайн максималды кернеумен көзді таңдауға бағытталған, сондықтан соңғы максималды мәнді сақтай отырып және оны кірістегі келесі мәнмен салыстыру кезінде сканерлеу бүкіл массивте жүргізіледі (ол сканерлеудегі келесі кернеу көзіне жатады).

Келесіде біз барлық кірістер бойынша мультиплекстеудің толық тізбегін «сканерлеу» немесе «цикл» деп атаймыз.

Екі мәнді салыстыру ACMP компоненттерінің көмегімен жүргізілмейді (алайда SLG46620G -де бар), керісінше мәндер цифрланған кезде DCMP модулімен. Бұл жетілдірілген және жетілдірілген әдіс, бірінші кезекте сілтемеде айтылады.

2 -суретте SLG46620G осы конструкция үшін қалай құрылымдалғандығы көрсетілген.

Аналогты кіріс сигналы ADG кірісіне PGA компоненті арқылы 1-ші кірістілікпен түседі. Әр түрлі кіріс параметрлері кіріс кернеулерін 0-1 В дейін салыстыруға арналған алдыңғы кондиционерлік электроникамен ең жақсы сәйкестікті табуға мүмкіндік береді. GreenPAK ADC модулінің ауқымы.

ADC біржақты режимде жұмыс істейді және аналогтық сигналды 8-разрядты цифрлық кодқа түрлендіреді, содан кейін ол DCMP модуліне беріледі. Сандық код ADC/FSM буфері ретінде конфигурацияланған SPI блогына беріледі, онда SPI CLK кірісіне келесі импульс келмейінше цифрлық код сақталуы мүмкін және өзгермейді. Бөлінген логикалық блок SPI CLK кірісін басқаратынын ескеріңіз. Біз бұл бөлікті кейінірек зерттейміз, себебі бұл дұрыс жұмыс істеу үшін жауап беретін «негізгі» логика. Жаңа сандық код SPI модулінде нақты максималды кіріс кернеуіне жататын жағдайда ғана сақталады.

DCMP компоненті ағымдағы ADC деректерін SPI блогында сақталатын соңғы жеңімпазбен (яғни соңғы табылған максимум) салыстыру үшін қолданылады. Жаңа ADC деректері алдыңғы мәліметтерден үлкен болғанда, OUT+ шығысында импульс тудырады. Біз OUT+ сигналын SPI блогын жаңа жеңімпазбен жаңарту үшін қолданамыз.

Жаһандық сағаттық сигнал ADC түрлендірулерін және жалпы уақытты басқарады. Түрлендіру жүргізілгеннен кейін, ADC параллельді шығысымен уақыт бойынша үйлестірілген ADC INT сигналының импульсі. Біз INT шығысын Matrix1-де DFFs енгізген 3 биттік екілік есептегішті ұлғайту үшін де қолданамыз, ол үш себеп бойынша пайдалы:

1. Есептегіштердің шығыс сызықтары сыртқы аналогтық мультиплексорға бағытталады, осылайша келесі кіріс кернеуін ADC -ке қызмет етеді;

2. Сканерлеу кезінде уақытша жеңімпазды сақтау үшін санау 3-разрядты тіркелген (Matrix1-де енгізілген);

3. Сканерлеу аяқталғаннан кейін санау екінші 3-разрядты (Matrix0-де енгізілген) жаңарту үшін декодталған.

3 -қадам: Логиканы енгізу

ADC модулі дәйекті түрде барлық кіріс кернеулерінің түрлендірілген деректерін бірінен соң бірін шексіз береді. Мультиплексор 0b111 (ондық 7) адресін алғаннан кейін, санауыш 0b000 (ондық ондық) мәніне ауысады, осылайша кіріс кернеулерінің жаңа сканерлеуін бастайды.

Сканерлеу кезінде параллель деректер шығысы жарамды болғанда ADC INT шығыс сигналы жасалады. Бұл сигнал импульстелген кезде аналогтық мультиплексор PGA -ға сәйкес кернеуді қамтамасыз ететін келесі кіріске ауысуы керек. Демек, ADC INT шығысы 3-биттік параллель шығыс сөзі сыртқы аналогтық мультиплексорға тікелей бағытталатын 2-суреттегі 3-разрядты екілік санауыштың тура сағаттық сигналы болып табылады (1-суреттегі «V таңдау»).

Енді кіріс кернеулері келесі қатынаста болуы керек мысалға жүгінейік:

а) V0 <V1 <V2

б) V2> V3, V4

c) V5> V2

3-сурет максималды шешім механизміне қатысатын негізгі сигналдарды көрсетеді.

Деректер ақыры SPI буферлік регистріне INT импульсімен синхронды түрде енгізілгендіктен, SPI буферінің мазмұны келесі ADC түрлендіру нәтижесімен салыстырылатын салыстыру терезесі бар. Бұл нақты уақыт DCMP шығысында OUT+ импульсінің пайда болуына әкеледі. Біз SPI буферлік регистріне жаңа мәндерді жүктеу үшін осы импульстарды пайдалана аламыз.

Алдыңғы суреттегі SPI буферлік деректер желісінен көрініп тұрғандай, SPI регистрі әрқашан уақыт бойынша 8 кірістің ең үлкен мәнін қамтиды және ол DCMP модулі үлкен мәнді анықтағанда ғана жаңартылады (DCMP сілтемесі) Сюжеттің OUT+ шығыс сызығы, жетіспейтін импульстар V2 -дің V5 -пен салыстырғанда регистрде бекітілуін сақтайды).

4 -қадам: тығырықтан шығу

Егер енгізілген логика жоғарыда сипатталғандай болса, біз тығырыққа тірелетініміз анық: жүйе SPI буферлік регистрінде сақталатыннан жоғары кернеуді ғана анықтай алады.

Бұл кернеудің төмендеуі кезінде де жарамды, содан кейін осы уақытқа дейін төмен болатын ең жоғары кіріс: ол ешқашан анықталмайды. Бұл жағдай 4 -суретте жақсы түсіндірілген, мұнда тек 3 кіріс кернеуі бар айқындық.

2 -ші қайталау кезінде V3 төмендейді, ал V1 - нақты максималды кернеу. Бірақ DCMP модулі импульсті қамтамасыз етпейді, себебі SPI буферлік регистрінде сақталатын деректер (0,6 В сәйкес) V1 (0,4 В) сәйкес келетіннен үлкен.

Содан кейін жүйе «абсолютті» максималды табушы ретінде әрекет етеді және шығуды дұрыс жаңартпайды.

Бұл мәселені шешудің жақсы әдісі - жүйе барлық арналардың толық сұрау циклын аяқтаған кезде деректерді SPI аралық регистріне қайта жүктеу.

Шын мәнінде, егер бұл кірістегі кернеу әлі де ең жоғары болса, ештеңе өзгермейді және басқару қауіпсіз түрде жалғасады (жоғарыдағы 4 -суретке сілтеме жасай отырып, бұл 0 және 1 ілмектерді қайталау жағдайлары). Екінші жағынан, егер кездейсоқ осы кірістегі кернеу басқа кірістен төмен мәнге дейін төмендесе, онда мәнді қайта жүктеу DCMP модуліне жаңа максималды мәнмен салыстыру кезінде OUT+ импульсін шығаруға мүмкіндік береді. 2 және 3 цикл қайталануларының жағдайы).

Мәселені шешу үшін логикалық схема қажет. Ол цикл нақты максималды кіріске жеткенде SPI компонентіне сағаттық сигнал беруі керек, осылайша оның жаңартылған деректер сөзін SPI аралық регистріне қайта жүктеуге мәжбүр етеді. Бұл төмендегі 7.2 және 7.6 бөлімдерде талқыланатын болады.

5 -қадам: құрылғы конфигурациясы - Matrix0 схемасы

SLG46620G -де 2 -суретте көрсетілгендей екі матрицалық блок бар. Келесі суреттер құрылғыға сәйкес конфигурацияларды көрсетеді.

Схеманың жоғарғы бөлігі - бұл 3 DFF (DFF0, DFF1 және DFF2) көмегімен жүзеге асырылатын «циклдік регистр». Кіріс мультиплексорының әрбір циклінен кейін 7 сегментті дисплей драйверіне «жеңімпаздың» екілік нөмірін жіберу жаңартылады, яғни соңғы сканерлеудегі ең жоғары кернеуі бар кіріс. DFF -тің сағаты да, деректер де Matrix1 -де сәйкесінше P12, P13, P14 және P15 порттары арқылы енгізілген логикадан келеді.

Төменгі бөлігі - аналогтық алдыңғы жағы, Pin 8 кірісі және x1 кірісі бар PGA. ADC INT шығысы SPI сағаттық логикасына да, P0 порты арқылы Matrix1 -ге де барады, онда ол есептегіш үшін сағаттық сигнал ретінде қызмет етеді.

ADC және SPI параллель деректер шығуы Matrix1 -де DCMP компонентіне қосылу үшін сәйкесінше NET11 және NET15 деп белгіленеді.

6 -қадам: Құрылғыны конфигурациялау - SPI Clocking Logic

Бұрын «Логикалық іске асыру» бөлімінде айтылғандай, SPI буферлік тізілімі нақты сақталған мән мен жаңа ADC түрлендіру деректері арасындағы салыстыру DCMP OUT+ шығысында импульс тудыратын сайын жаңартылады.

Егер сигнал ADC INT шығысымен ЖӘНЕ өңделсе, сигналдың тұтастығы қамтамасыз етіледі. Бұл кез келген серпіліс пен жалған триггерді болдырмайды.

Біз сондай -ақ, тұйық жағдайларды өткізіп жіберу үшін, цикл нақты жеңімпаз деректеріне жеткенде, SPI буферін жаңарту қажет екенін атап өттік.

SPI -ді дұрыс өлшеу үшін ойында үш сигнал бар:

1. ADC INT шығысы (LUT0-IN1)

2. DCMP OUT+ шығысы (LUT0-IN0 P10 порты арқылы)

3. Санау бекіткіш сигналына тең (PUT порты арқылы LUT0-IN2)

Алғашқы екеуі AND-ed және екеуі де OR-ed, екіншісі LUT0-де, олардың орындалуы 6-суреттегідей конфигурацияланған.

7 -қадам: құрылғы конфигурациясы - Matrix0 компоненттерінің қасиеттері

7-10 суреттер Matrix0 тиесілі қалған компоненттердің қасиеттер терезелерін көрсетеді.

8 -қадам: құрылғы конфигурациясы - Matrix1 схемасы

9 -қадам: құрылғы конфигурациясы - 3 биттік екілік санауыш

Схеманың жоғарғы бөлігінде логикалық элементтер бар, негізінен 3-разрядты ADC INT шығысымен есептелген екілік санауыш. Бұл есептегіш 12 -суретте көрсетілген «стандартты» схемамен орындалады.

Бұл есептегіш біздің дизайнда Flip-Flops DFF9, DFF10, DFF11 және INV1, LUT4, LUT8 көмегімен жүзеге асады. DFF9 шығысы - бұл LSB, ал DFF11 - бұл MSB, 13 -суретте көрсетілгендей.

LUT4 XOR ретінде конфигурацияланған, ал LUT8 12-суреттегі AND-XOR логикасын орындайды.

Сыртқы аналогтық мультиплексорды шешу үшін санауыштың шығысы үш цифрлық шығыс түйреуішіне өтеді.

LUT10 сканерлеу аяқталғанда есептегіш кодын шифрлайды және импульсті Matrix0 -ге DLY8 мен P12 порты арқылы береді. Бұл санауыштың шығуын AND енгізу арқылы жүзеге асады, осылайша 7 dec (0b111 екілік, цикл соңы) нөмірін декодтау.

10 -қадам: Құрылғы конфигурациясы - 3 биттік салыстыру логикасы

15 -суретте циклдің ағымдағы «жеңімпаз» мекен -жайында қайталануын анықтау үшін қолданылатын схема көрсетілген. Бұл жағдайда, жоғарыда талқыланғандай, цифрлық импульс ықтимал тығырықтағы жағдайды шешу үшін ағымдағы ADC нәтижесін қайта жүктеуге мәжбүр етуі керек.

«Жеңімпаз» адресі Matrix1 уақытша тізілімінде сақталады (төменде қараңыз), ал ағымдағы адресті екілік санауыш шығарады.

XNOR қақпалары екі кіріс тең болғанда шынайы (логикалық 1 немесе «жоғары») шығуды қамтамасыз етеді. ЖӘНЕ бұл сигнал барлық биттерге (LUT9) қос екілік код бірдей болған кезде бізге импульс береді. XOR қақпалары туралы толық ақпаратты тексеруші ретінде Анықтамадан табуға болады.

«Counter-equals-Latch» сигналы Matrix0-ге P11 порты арқылы беріледі.

11 -қадам: Құрылғыны конфигурациялау - сандық салыстыру логикасы және уақытша тіркеу

11-суреттің төменгі бөлігі (16-суретте көрсетілген) DCMP блогын көрсетеді, бұл дизайнның шешім қабылдайтын бөлігі.

DFF6, 7 және 8 цикл жұмыс істеп тұрған кезде «жеңімпаз» уақытша енгізу нөмірін сақтау үшін 3-разрядты регистр құрайды. Айналым үшін енгізу 3-разрядты екілік есептегіштер болып табылады, олар 11-суреттің жаһандық Matrix1 схемасында көрінеді, мұнда түсінікті болу үшін өткізіп жіберілген.

Бұл регистрдің шығысы 7 сегментті дисплейді тікелей басқара алмайды, себебі мұнда сақталған мән сканерлеу кезінде өзгереді және сканерлеудің соңында ғана «жарамды» деп есептелуі керек.

Осы себепті, уақытша регистрдің шығысы Matrix0 Loop Register-ке матрицалық P13, P14 және P15 порттары арқылы қосылады.

16-суретте ADC-SPI регистрлерінің салыстыру нәтижелері жаңа табылған максималды нәтижеге жеткенде уақытша регистр DCMP OUT+ шығысымен сағатталатынын байқау маңызды.

Сол OUT+ сигналы Matrix0, SPI CLK Logic, P10 порт арқылы беріледі.

12 -қадам: Құрылғы конфигурациясы - Matrix1 компоненттерінің қасиеттері

17-19-суреттер Matrix1-ге тиесілі компоненттердің қасиеттерінің терезелерін көрсетеді.

13 -қадам: Нәтижелер

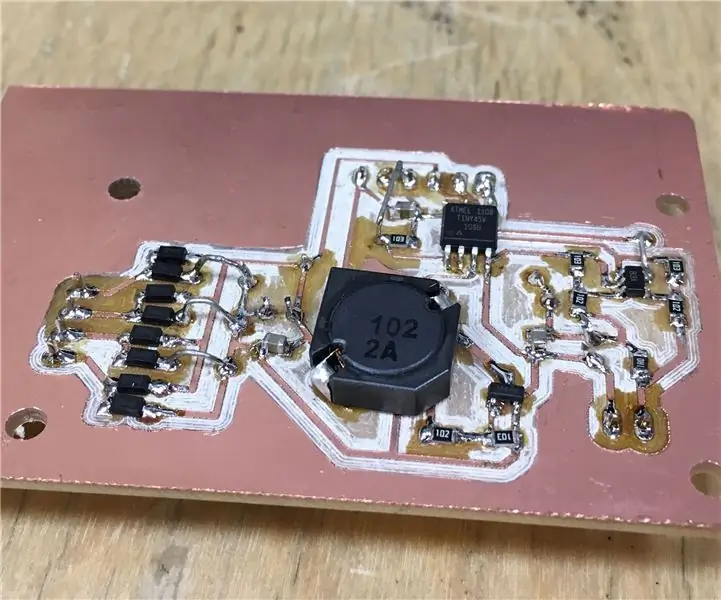

Іске асыруды тексеру үшін бағалау тақтасының прототипі құрастырылды, онда 8 аналогтық кіріс кернеуі TrimPots көмегімен резисторлық бөлгіштер сериясы арқылы алынады (20 -суретте көрсетілгендей).

Қолданылатын мультиплексор - бұл ADG508, бір бөлікпен жұмыс жасай алатын бөлік (12 В).

7 сегментті дисплей драйвері-74LS47. Ол параллель енгізу сөзінің кодын шешеді және 7 анодты жалпы анодты дисплейді басқарады.

Бағалау тақтасында 21-суретте көрсетілгендей кеңейту коннекторында GreenPAK Advanced Development Platform-ге тікелей қосылатын 2x10 тік бұрышты қосқышы бар.

GreenPAK Advanced Development Platform -мен бірге жылдам тексеру үшін сигналдарды өлшеуді жеңілдетеді. Мысалы, 22 -суретте HP 54620A логикалық анализаторы түсірген сигналдар жиынтығы (сәйкесінше CLOCK, ADC INT шығысы және DCMP OUT+ шығысы) көрсетілген. Толқындық формалар OUT+ сигналының жоғарылау жиегімен іске қосылады («A> B» деп белгіленген), сондықтан аналогтық кірістер арасында жаңа максималды кернеу анықталған кезде бұл толқындық пішінді түсіру болып табылады. Шын мәнінде, ол 22 -суретте көрсетілген сәйкес кернеуді жоғарылату үшін Бағалау тақтасының TrimPots бірінің айналуы арқылы алынды.

23 -суретте Бағалау тақтасының схемасы көрсетілген.

Қорытынды

Бұл нұсқаулықта біз көп каналды басқару жүйелеріне жалпы қосымша ретінде қолданылатын сегізарналы максималды (немесе мин) кернеуді тапқышты енгіздік. Ұсынылған әдіс GreenPAK компоненттерінің жетілдірілген мүмкіндіктерін пайдаланады және аналогтық және цифрлық функцияларды бір чипке қалай қосуға болатынын көрсетеді. Қолданбаның көлемі мен құнын төмендету үшін бірнеше коммерциялық IC -ді Dialog GreenPAK -ке ауыстыруға болады.

Ұсынылған:

Жоғары кернеулі батареялар үшін кернеу мониторы: 3 қадам (суреттермен)

Жоғары вольтты аккумуляторларға арналған кернеу мониторы: Бұл нұсқаулықта мен сізге электрлік ұзын тақтаның батарея кернеу мониторын қалай құрастырғанымды түсіндіремін. Оны қалағаныңызша орнатыңыз және батареяға тек екі сымды қосыңыз (Gnd және Vcc). Бұл нұсқаулықта сіздің аккумуляторыңыздың кернеуі 30 вольттан асады деп болжанған

Шағын жел турбиналары үшін максималды Power Point трекері: 8 қадам

Кіші жел турбиналары үшін максималды Power Point трекері: Интернетте DIY жел турбинасы көп, бірақ олардың нәтижесін қуат немесе энергия тұрғысынан нақты түсіндіретіндер аз. Сонымен қатар, қуат, кернеу мен ток арасында жиі шатасулар болады. Көп адамдар айтады: " Мен өлшеймін

Компьютерге немесе үйге арналған 8 арналы аналогтық күшейткіш: 12 қадам (суреттермен)

Компьютерге немесе үй театрына арналған 8 арналы аналогтық күшейткіш: Бұл менің бірінші нұсқаулығым. Мен сізге бөлек аналогтық шығысы бар компьютерге немесе аудио жүйеге 8 каналды күшейткішті қалай жасау керектігін үйретемін, мен оны жұмыс үстелі компьютерімде, фильмдерді қарауда, HD музыкасын тыңдауда және ойындар ойнауда қолдандым

5 мин usb үстел үсті шам үйі: 7 қадам

Үстел үстіндегі 5 минуттық шамдар үйі: Бұл нұсқаулықта мен сізге USB үстелінің үстіңгі тақтайшасын қалай қызықты етіп жасау керектігін көрсетемін. түсініктеме беріңіз

10 мин. Star Trek Phaser Flashing LED режимі: 7 қадам

10 мин. Star Trek Phaser Flashing LED режимі: Мен досым Энди туралы ойладым, мен Playmates Classic Star Trek Phaser -ді енгіздім. Бұл таңқаларлықтай тез және оңай орындалды. Мен Blu-Ray лазерлік фазерлік модуль сияқты қауіпті емес, әлдеқайда жақсы көрінетін нәрсені алғым келді (B емес